# UNIVERSITÀ DEGLI STUDI DI PARMA FACOLTÀ DI INGEGNERIA

# Corso di Reti Logiche A

anno accademico 2006-2007 prof. Stefano CASELLI prof. William FORNACIARI

# I compitino del 16 novembre 2006

# Bozza soluzioni del 16.11.2006

| Cognome (LEGGIBILE)Nome (LEGGIBILE)                                                   |  |  |  |  |  |

|---------------------------------------------------------------------------------------|--|--|--|--|--|

| Matricola Firma                                                                       |  |  |  |  |  |

| Corso di Laurea: $\square$ ing informatica; $\square$ telecom; $\square$ elettronica; |  |  |  |  |  |

| $\square$ teledidattico; $\square$ altro (specif)                                     |  |  |  |  |  |

| Professore di riferimento: □ CASELLI; □ FORNACIARI                                    |  |  |  |  |  |

Riportare i dati personali in modo che siano LEGGIBILI

| D1 | D2 | D3 | D4 | D5 | тот |

|----|----|----|----|----|-----|

| 7  | 9  | 5  | 4  | 8  | 33  |

# NOTE PER LO SVOLGIMENTO

Si raccomanda di essere sintetici (al fine di evitare inutili perdite di tempo in trattazioni generiche e poco significative ai fini della valutazione finale) e ordinati allo scopo di migliorare l'interpretazione da parte dei correttori.

I temi proposti debbono essere risolti utilizzando unicamente lo spazio lasciato al termine del testo di ogni quesito, il retro delle pagine o, eventualmente, utilizzando lo spazio finale. Verranno corretti SOLO i fogli componenti il tema d'esame.

È vietato consultare testi o appunti di qualunque genere così come interagire con i vicini. Chiunque sia trovato in possesso di materiale relativo al corso, anche se non strettamente attinente al tema d'esame, vedrà annullata la prova.

Data la seguente funzione logica non completamente specificata con 4 variabili di ingresso A,B,C,D e un bit di uscita Z, se ne effettui la sintesi multilivello mediante scomposizione semplice disgiuntiva e si realizzi il circuito corrispondente utilizzando esclusivamente porte NOR. Si riportino tutti i passaggi ed il disegno del circuito finale.

| Α | В | С | D | uscita Z |

|---|---|---|---|----------|

| 0 | 0 | 0 | 0 | 1        |

| 0 | 0 | 0 | 1 | X        |

| 0 | 0 | 1 | 1 | 1        |

| 0 | 0 | 1 | 0 | 1        |

| 0 | 1 | 0 | 1 | 1        |

| 0 | 1 | 1 | 0 | X        |

| 1 | 1 | 0 | 1 | X        |

| 1 | 0 | 0 | 0 | 1        |

| 1 | 0 | 1 | 1 | X        |

Le rimanenti configurazioni corrispondono al valore 0 dell'uscita.

#### Soluzione

Mappa di Karnaugh corrispondente alla funzione assegnata:

| CD | 00 | 01 | 11 | 10 |

|----|----|----|----|----|

| AB |    |    |    |    |

| 00 | 1  | X  | 1  | 1  |

| 01 |    | 1  |    | X  |

| 11 |    | X  |    |    |

| 10 | 1  |    | X  |    |

E' possibile attribuire valori alle condizioni di indifferenza in modo da pervenire alla seguente mappa di partizione, che indica la possibilità di utilizzare (C,D) come variabili vincolate:

|    | _  |    | •  |    |

|----|----|----|----|----|

| CD | 00 | 01 | 11 | 10 |

| AB |    |    |    |    |

| 00 | 1  | 1  | 1  | 1  |

| 01 |    | 1  |    | 1  |

| 11 |    | 0  |    |    |

| 10 | 1  |    | 1  |    |

Utilizzando come funzione di vincolamento quella realizzata per la riga AB=01, ed utilizzando una sintesi di tipo PS per ricavare un'espressione NOR si ha:  $h=(C+D)(C'+D')=(C\downarrow D)\downarrow (C'\downarrow D')$

| h  | 0 | 1 |

|----|---|---|

| AB |   |   |

| 00 | 1 | 1 |

| 01 | 0 | 1 |

| 11 | 0 | 0 |

| 10 | 1 | 0 |

Da cui:  $Z=(B'+h)(A'+h')=(B'\downarrow h)\downarrow (A'\downarrow h')$

L'esercizio richiede infine di disegnare il circuito multilivello risultante.

Data la seguente tabella di verità di una funzione a due valori (F1, F2) di 4 variabili indipendenti (A, B, C, D), riportare, trascrivendo tutti i passaggi:

- Il risultato della **prima fase** del metodo di Quine-McCluskey multi-uscita, ovvero la ricerca degli implicanti primi. Riportare anche le espressioni degli implicanti primi. Suggerimento: servirsi delle mappe di Karnaugh per verificare il risultato.

- La **seconda fase** del metodo, ovvero la ricerca della copertura ottima per F1 ed F2, commentando i vari passaggi. Riportare anche le espressioni ottime per F1 e F2.

| mintermine | Α | В | С | D | Uscita F1 | Uscita F2 |

|------------|---|---|---|---|-----------|-----------|

| 0          | 0 | 0 | 0 | 0 |           | 1         |

| 1          | 0 | 0 | 0 | 1 |           |           |

| 2          | 0 | 0 | 1 | 0 | 1         | 1         |

| 3          | 0 | 0 | 1 | 1 |           |           |

| 4          | 0 | 1 | 0 | 0 | 1         |           |

| 5          | 0 | 1 | 0 | 1 | 1         | 1         |

| 6          | 0 | 1 | 1 | 0 | 1         | 1         |

| 7          | 0 | 1 | 1 | 1 | 1         | 1         |

| 8          | 1 | 0 | 0 | 0 |           | 1         |

| 9          | 1 | 0 | 0 | 1 |           |           |

| 10         | 1 | 0 | 1 | 0 | 1         | 1         |

| 11         | 1 | 0 | 1 | 1 |           |           |

| 12         | 1 | 1 | 0 | 0 | 1         |           |

| 13         | 1 | 1 | 0 | 1 | 1         |           |

| 14         | 1 | 1 | 1 | 0 | 1         | 1         |

| 15         | 1 | 1 | 1 | 1 |           |           |

# Soluzione

| M0  | 0000 01 | •     | 00-0 01 | 0,2,8,10 -0-0  | 01 | P3=b'd' |

|-----|---------|-------|---------|----------------|----|---------|

| М2  | 0010 11 |       |         | - 2,6,10,1410  | 11 | P4=cd'  |

| M4  | 0100 10 | 2,6   | 0-10 11 | 4,5,6,7 01     | 10 | P5=a'b  |

| M8  | 1000 01 | 2,10  | -010 11 | 4,5,12,13 -10- | 10 | P6=bc'  |

|     |         | 4,5   | 010- 10 | 4,6,12,14 -1-0 | 10 | P7=bd'  |

| M5  | 0101 11 | 4,6   | 01-0 10 |                |    |         |

| Мб  | 0110 11 | 4,12  | -100 10 |                |    |         |

| M10 | 1010 11 | 8,10  | 10-0 01 |                |    |         |

| M12 | 1100 10 |       |         | _              |    |         |

|     |         | 5,7   | 01-1 11 | P1=a'bd        |    |         |

| М7  | 0111 11 | 5,13  | -101 10 |                |    |         |

| M13 | 1101 10 | 6,7   | 011- 11 | P2=a'bc        |    |         |

| M14 | 1110 11 | 6,14  | -110 11 |                |    |         |

|     |         | 10,14 | 1-10 11 |                |    |         |

|     |         | 12,13 | 110- 10 |                |    |         |

|     |         | 12,14 | 11-0 10 |                |    |         |

#### Copertura

Si costruisce la tabella di copertura. Si osserva che P4 è essenziale per F1 e F2. P6 è essenziale per F1. P3 è essenziale per F2. P1 è essenziale per F2 ma non per F1: la riga corrispondente non può essere eliminata, tuttavia il suo costo può essere posto a 0.

Eliminando le righe e le colonne relative a P4, P6, P3, e le colonne di F2 per P1, si ottiene una tabella ridotta che ha una sola colonna (il mintermine 7 di F1). Tale colonna può essere coperta con costo pari a 0 dall'implicante P1 già selezionato per F2.

Le espressioni ottime pertanto sono: F1=P1+P4+P6=a'bd+cd'+bc' F2=P1+P3+P4=a'bd+b'd'+cd'

### **Quesito D3**

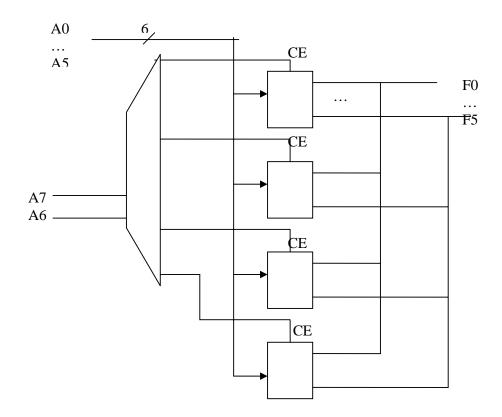

Si supponga che sia disponibile la descrizione mediante tabella di verità di 6 funzioni logiche (F0..F5) dipendenti da 8 variabili di ingresso A7, ...,A0. Si presenti lo schema logico di un circuito in grado di realizzare tali funzioni facendo uso di memorie ROM con 6 bit di indirizzamento e con larghezza di parola di 8 bit dotate di segnale di controllo CE (chip enable). Il segnale CE, attivo alto, consente di porre le uscite nello stato di alta impedenza.

Si disegni l'architettura globale del sistema digitale, evidenziando con chiarezza gli ingressi e le uscite delle ROM, gli eventuali componenti aggiuntivi e le interconnessioni tra i componenti utilizzati. Si delinei inoltre il procedimento che porta alla determinazione dei contenuti delle parole da inserire nella ROM a partire dalla tabella della verità delle funzioni assegnate.

#### Soluzione

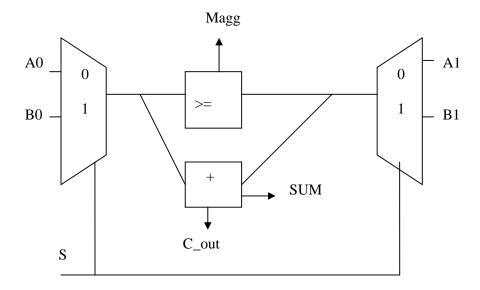

Si deve realizzare un circuito dotato di 4 ingressi principali A0, A1, B0, B1, di un ingresso di selezione S e di tre uscite SUM, C\_out, Magg, facendo **uso di sole porte logiche.**

La progettazione parte da un sistema precedente, riportato in figura, formato da due multiplexer e da due blocchi funzionali che operano in parallelo: un comparatore e un sommatore il cui riporto in ingresso è fissato a zero. Tale circuito, in base al valore della variabile di selezione S, forniva in ingresso ai due blocchi funzionali gli ingressi Ai o i Bi.

Il nuovo circuito deve operare in modo parzialmente differente: l'uso dei due blocchi funzionali deve avvenire in mutua esclusione e, quando uno dei due e' attivo, la/le uscite dell'altro debbono essere a zero. In altri termini:

Se S=0, allora SUM=A1+A0; C\_out= riporto della somma precedente; Magg=0; Se S=1, allora Cout=SUM=0; Magg=1 se B1>=B0.

Progettare e disegnare una rete logiche corrispondente a tale specifica facendo uso di sole porte logiche. Si riportino i passaggi, le ipotesi adottate e il disegno del circuito finale

#### Soluzione

SUM=(A1'A0+A1A0') S' Cout=A1 A0 S' Magg=(B1+B0') S

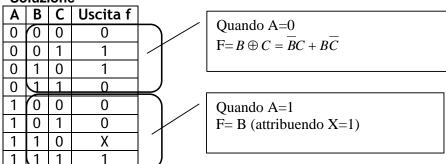

Data la seguente tabella di verità:

- Sintetizzare la rete logica corrispondente facendo obbligatoriamente uso di un multiplexer a due vie e porte logiche. Riportare sia le equazioni logiche, sia la rete complessiva, evidenziando con chiarezza gli ingressi del Multiplexer e la variabile di selezione usata.

- 2. Realizzare la stessa funzione logica facendo uso del minimo numero di porte **NOR** a 2 ingressi.

- 3. Considerando la realizzazione del MUX effettuata tramite porte logiche, come mostrato a lezione e sui testi, confrontare la **velocità** della realizzazione tramite MUX con quella basata sul minimo numero di porte logiche NOR.

- 4. Analizzare il **costo** per una realizzazione a componenti discreti, misurato come numero di circuiti integrati (ovvero il MUX ha un costo unitario).

| Α | В | С | Uscita f |

|---|---|---|----------|

| 0 | 0 | 0 | 0        |

| 0 | 0 | 1 | 1        |

| 0 | 1 | 0 | 1        |

| 0 | 1 | 1 | 0        |

| 1 | 0 | 0 | 0        |

| 1 | 0 | 1 | 0        |

| 1 | 1 | 0 | Χ        |

| 1 | 1 | 1 | 1        |

#### Soluzione

Scelgo di usare A come variabile di selezione

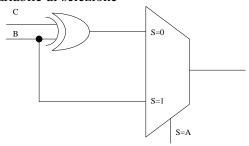

La espressione minima PS è: f=(B+C)(A'+B)(A+B'+C') che realizzata tramite NOR diviene:  $f=(B\downarrow C)\downarrow (A'\downarrow B)\downarrow (A\downarrow B'\downarrow C')$

-> quattro porte NOR

La rete con il MUX ha 4 livelli e ovviamente è più lenta rispetto a quella a NOR che comunque ha solo due livelli (trascurando il ritardo dei NOT, come di consueto). Circa il costo, nel caso lo XOR costi uno allora la prima soluzione è più economica, nel caso invece lo XOR sia fatto con porte logiche allora il costo complessivo diviene 4 ed è uguale.